- 软件大小:3481.59M

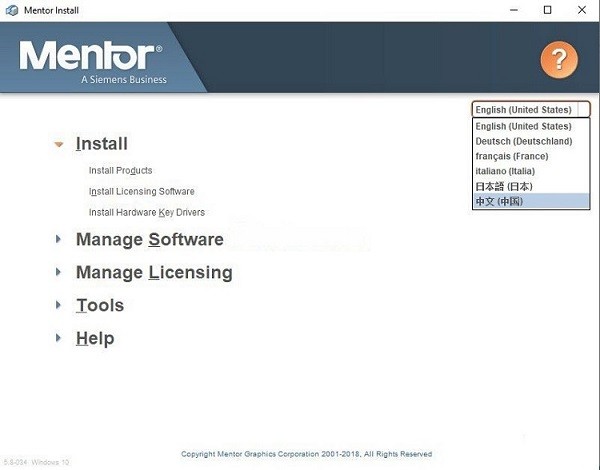

- 软件语言:中文

- 软件类型:国产软件

- 软件类别:免费软件 / 其他行业

- 更新时间:2022-01-15 17:24

- 运行环境:WinAll, Win7

- 软件等级:

- 软件厂商:

- 官方网站:暂无

2KB/中文/0.5

240.00M/中文/2.5

11.58M/中文/2.5

87.20M/中文/8.0

15.47M/中文/0.7

mentor graphics软件可以进行各种电路设计,还可以在线进行测试,打造全新数据分析系统,可以模拟真实电路,内置多种工具可以快速画图,保存历史编辑信息,超多资源可以直接使用,模拟进行各种测试。

新技术可提供可视化显示、布局和3D设计规则检查,帮助机械和制造团队最大限度地减少设计迭代。原理图设计和布局增强功能可提高整个流程范围内的可用性,进而提高用户生产率。

使用简单:

产品线提供一套可立即使用的解决方案,能自动转换旧规则档案,並在结果显示环境內( RVE)以图形操作方式轻易完成除错工作,故能整合至任何设计环境。简单又强健可靠的规则档案语法让程式设计更容易。

庞大处理容量:

对於阶层式设计的处理容量几乎毫无限制,2GB或更多的记忆体存取能力可以协助客户发展大型设计专案;它也支援64位元作业系统,並提供4GB以上定址能力,多绪执行选项可以大幅提升工作效能,而且每颗处理器只须增加1-2%记忆体。

最佳工作效能:

採用高效率处理引擎,可在数小时內提供扁平式与阶层式演算法的咚憬Y果,不像以前需要数天时间;另外还有多绪执行的功能选项,可大幅增加验证速度。

与设计方式无关:

只有验证工具才能针对所有设计方式,提供操作简单的全自动阶层分析与最佳化能力,不但让执行过程更有效率,也不会影响工作效能。

最佳化的可製造性处理能力:

所有设计规则检查工具中,只有完全整合晶片与佈局对比检查,可自动找出微影程序问题;它提供先进的天线检查能力、自动的平坦化填充功能(planarization fill)和以规则为基础的光学製程修正,为使用者带来一套完整的可製造性处理流程。

ASIC原型支持

简化ASIC到FPGA的迁移

对Atmel和QuickLogic的OEM支持

所有设备都具有相同的HDL和约束

与Mentor Tools集成

使用HDL Designer重用设计

使用FormalPro进行等效性检查

简ASIC到FPGA的迁移

自动门控时钟转换

DesignWare实例转换

支持ASIC时序约束(SDC)

ASIC原型支持

FPGA供应商的独立集成

支持Altera,Lattice,Microsemi和Xilinx

自动门控时钟转换

FPGA系列的高质量结果(QoR)。

此外,Mentor Graphics还与领先的IP供应商合作,提供多种经验证,可与Precision Synthesis一起使用。

物理合成

Precision RTL Plus提供多厂商物理综合,使设计人员能够更快地实现他们的时序目标,并减少迭代次数。 通过支持来自所有主要设备供应商的超过25个FPGA系列,物理综合是一种按键和时序驱动技术,为FPGA供应商的布局布线(P&R)工具提供优化的网表。 精确的物理合成可将平均Fmax提高10%,范围从5%到40%不等。

低功耗合成

由于更多的FPGA正在转向低功耗应用,因此设计人员不仅需要仔细选择功耗最高的器件,还必须确保其实现流程尽可能降低功耗。 Precision RTL Plus支持各种优化,可降低多个设备供应商的动态功耗。

增量合成

Precision RTL Plus使设计人员能够通过使用全自动或基于分区的增量流快速且可预测地实施更改,从而减少运行时间并保留已完成的工作。全自动增量合成不需要预分区,可将运行时间缩短60%,与Xilinx一起使用时可节省更多的运行时间? SmartGuideTM(Xilinx增量P&R流量)。基于分区的增量合成是基于团队的设计方法的理想选择,可以对子分区进行本地化更改,并提供最多6倍的运行时间缩减。

Precise-IP TM:FPGA供应商独立IP平台

作为完整的FPGA供应商独立方法的一部分,Precision RTL Plus采用Precise-IPTM,这是一个平台设计人员,可以生成多种预先验证的IP,以实现跨不同

提取码:e25w

请描述您所遇到的错误,我们将尽快予以修正,谢谢!

*必填项,请输入内容