- 软件大小:150.00M

- 软件语言:中文

- 软件类型:汉化软件

- 软件类别:修改软件 / 其他行业

- 更新时间:2023-03-24 09:47

- 运行环境:WinAll, WinXP, Win7, Win8, Win10

- 软件等级:

- 软件厂商:

- 官方网站:暂无

26.08M/中文/10.0

506.00M/中文/0.7

2631.67M/中文/0.0

4.44M/中文/10.0

9.79M/中文/5.3

cadence17.2其全称是Cadence Allegro SPB Orcad17.2,这是一款专业的电路仿真软件,这款软件功能强大,应用广泛,使用简单方便,需要的朋友欢迎来绿色资源网下载使用!

cadence spb 17.2涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,pcb设计和硬件仿真建模等。同时,Cadence公司还提供设计方法学服务,帮助客户优化其设计流程;提供设计外包服务,协助客户进入新的市场领域。

板级电路设计系统

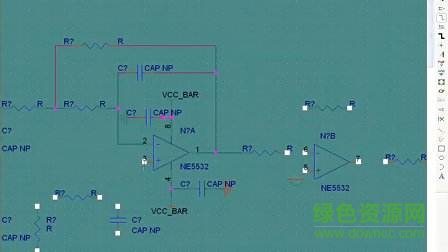

包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

Alta系统级无线设计

这一块的产品主要是应用于网络方面的,我个人以为。尤其是它包括有一套的gsm模型,很容易搞cdma等等之类的东西的开发。但是我觉得做信号处理和图象处理也可以用它,因为它里面内的spw太牛了,至少是看起来是,spw最牛的地方就是和hds的接口,和matlab的接口。matlab里面的很多模型可以直接调入spw,然后用hds生成c语言仿真代码或者是hdl语言仿真代码。

时序驱动的深亚微米设计

这部分是底层设计的软件。底层设计的工作我感觉是细活,来来回回是需要走很多次重复的流程的。在以前的设计流程中( .6um及其以上 ),一般情况下对于连线延时是可以不用考虑,或是说它们对设计的影响不算很大。在设计完成后,做一下pex,然后仿真一下,小设计的话,多半是可以通过的。

全定制ic设计工具

Virtuoso Schematic Composer : IC Design Entry 它是可以进行混合输入的原理图输入方式。支持 vhdl/hdl语言的文本输入。

逻辑设计规划器

这是用于设计早期的规划工具。其主要用途是延时预测、生成供综合工具使用的线路负载模型。这个工具是用来在物理设计的早期象逻辑设计者提供设计的物理信息。

物理设计规划器

物理设计的前期规划。对于大型设计而言,物理设计的前期规划非常重要。很多流程中,在前期的物理规划(floorplan)结束后,就需要一次反标验证设计的时序。

1.拥有系统级设计,功能验证,IC综合及布局布线。

2.拥有模拟、混合信号及射频IC设计,全定制集成电路设计。

3.拥有IC物理验证,PCB设计和硬件仿真建模等功能。

4.拥有文件,安装后就可以进行电子的设计和开发了。

5.系统互连平台能够跨集成电路、封装和PCB协同设计高性能互连。

6.应用平台的协同设计方法,工程师可以迅速优化I/O缓冲器之间和跨集成电路、封装和PCB的系统互联。

7.该方法能避免硬件返工并降低硬件成本和缩短设计周期。

8.约束驱动的Allegro流程包括高级功能用于设计捕捉、信号完整性和物理实现。

9.由于它还得到Cadence Encounter与Virtuoso平台的支持。

10.Allegro协同设计方法使得高效的设计链协同成为现实。

请描述您所遇到的错误,我们将尽快予以修正,谢谢!

*必填项,请输入内容